差分放大結(jié)構(gòu)作為模擬射頻集成電路設(shè)計中的核心技術(shù),在現(xiàn)代通信系統(tǒng)和無線應(yīng)用中發(fā)揮著至關(guān)重要的作用。憑借其優(yōu)異的共模噪聲抑制能力和抗干擾特性,差分結(jié)構(gòu)已成為RF IC設(shè)計的首選方案之一。

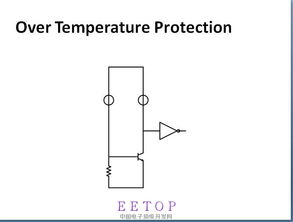

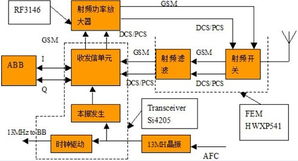

在RF集成電路設(shè)計中,差分放大器的優(yōu)點主要體現(xiàn)在三個方面:它能有效抑制電源噪聲和襯底耦合帶來的干擾,這對高頻工作環(huán)境尤為重要;雙端輸入特性使其能夠直接處理平衡信號,無需額外的單端轉(zhuǎn)差分電路;在工藝偏差和溫度變化條件下,差分結(jié)構(gòu)表現(xiàn)出更好的穩(wěn)定性和匹配特性。

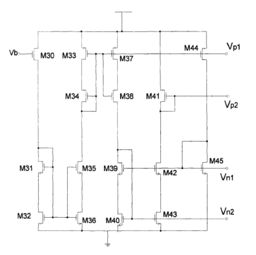

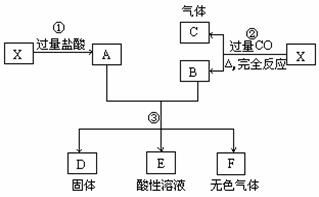

差分放大結(jié)構(gòu)也面臨著諸多設(shè)計挑戰(zhàn)。在RF頻段,差分對管的匹配精度直接影響電路的共模抑制比,這對版圖設(shè)計提出了極高要求。尾電流源的設(shè)計需要兼顧輸出阻抗和電壓余量,以確保足夠的共模抑制能力。在EETop等專業(yè)論壇的討論中,工程師們經(jīng)常就這些問題展開深入交流。

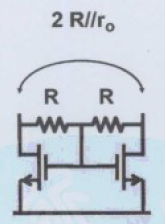

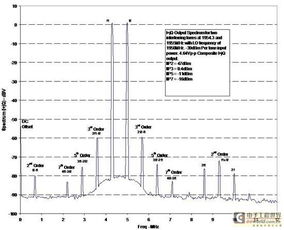

針對不同應(yīng)用場景,差分放大結(jié)構(gòu)衍生出多種變體,包括折疊共源共柵結(jié)構(gòu)、帶有有源負(fù)載的差分對以及全差分運放等。設(shè)計者需要根據(jù)具體的增益、帶寬、噪聲和線性度要求,選擇最合適的拓?fù)浣Y(jié)構(gòu)。

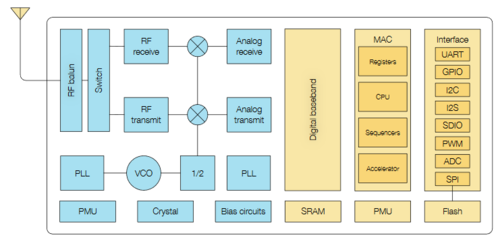

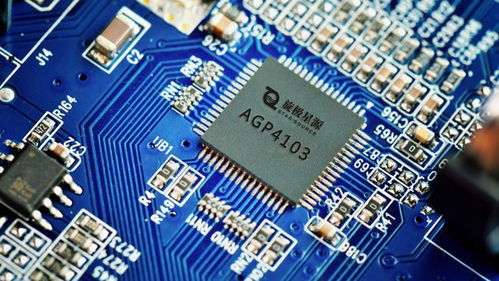

在嵌入式系統(tǒng)中,RF集成電路往往需要與數(shù)字電路集成在同一芯片上,這給差分放大器的設(shè)計帶來了額外的挑戰(zhàn)。襯底噪聲耦合、電源完整性和電磁兼容性問題都需要在設(shè)計階段充分考慮。

隨著5G、物聯(lián)網(wǎng)等新興應(yīng)用的普及,對RF集成電路的性能要求越來越高。差分放大結(jié)構(gòu)作為模擬前端的關(guān)鍵模塊,其設(shè)計技術(shù)將繼續(xù)演進,為半導(dǎo)體行業(yè)的發(fā)展提供堅實支撐。