在Analog/RF集成電路(IC)設(shè)計(jì)的宏大世界中,基準(zhǔn)電流源如同寂靜的燈塔,為紛繁復(fù)雜的模擬與射頻電路提供穩(wěn)定、精確的偏置與參考。它不僅是模擬電路設(shè)計(jì)的基石,更是衡量設(shè)計(jì)者功底深淺的關(guān)鍵。本文將探討如何手算基準(zhǔn)電流源,并以此為切入點(diǎn),結(jié)合全球最大最火的半導(dǎo)體集成電路社區(qū)之一——EETop,來(lái)討論Analog/RF IC設(shè)計(jì)的核心思想與實(shí)踐。

一、 基準(zhǔn)電流源:為何手算依然重要?

在EDA工具高度發(fā)達(dá)的今天,手算似乎顯得有些“復(fù)古”。對(duì)于Analog/RF IC設(shè)計(jì)師而言,手算絕非過(guò)時(shí),而是深入理解電路本質(zhì)、快速評(píng)估架構(gòu)可行性、進(jìn)行初始設(shè)計(jì)與優(yōu)化的必備技能。手算能幫助設(shè)計(jì)師:

- 建立直覺(jué):理解晶體管工作狀態(tài)(飽和區(qū)、線性區(qū)、亞閾值區(qū))、電阻、電容等元件如何協(xié)同工作,產(chǎn)生一個(gè)幾乎不受電源電壓和溫度影響的穩(wěn)定電流。

- 快速迭代:在架構(gòu)設(shè)計(jì)初期,通過(guò)簡(jiǎn)化的手算模型(如平方律模型、Gummel-Poon模型的部分簡(jiǎn)化)快速確定器件的大致尺寸(W/L),避免在仿真中盲目嘗試。

- 洞察本質(zhì):清晰看到基準(zhǔn)電流與工藝參數(shù)(如遷移率μ、氧化物電容Cox、閾值電壓Vth)、電阻絕對(duì)值以及電源電壓的關(guān)系,從而理解設(shè)計(jì)的魯棒性與工藝角(corner)下的變化。

二、 經(jīng)典結(jié)構(gòu)的手算解析:以ΔVgs基準(zhǔn)電流源為例

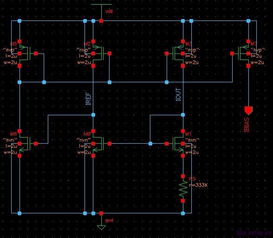

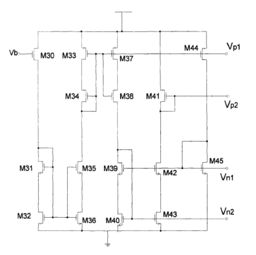

一個(gè)經(jīng)典且廣泛使用的基準(zhǔn)電流源結(jié)構(gòu)是利用兩個(gè)工作在飽和區(qū)、具有不同寬長(zhǎng)比(或不同電流密度)的MOS管產(chǎn)生一個(gè)ΔVgs,并將此電壓施加在一個(gè)電阻R上,從而產(chǎn)生電流Iref。

基本結(jié)構(gòu)(以NMOS為例):

1. M1與M2的柵極和漏極短接(二極管連接),假設(shè)它們具有相同的長(zhǎng)度L,但寬度不同(W2 = n * W1)。

2. 一個(gè)運(yùn)放(或通過(guò)電流鏡強(qiáng)制)確保流過(guò)M1和M2的電流相同(均為Iref)。

3. M1的源極接地,M2的源極串聯(lián)一個(gè)電阻R后接地。

手算推導(dǎo)(忽略溝道長(zhǎng)度調(diào)制效應(yīng)λ):

對(duì)于飽和區(qū)MOS管,電流公式為:I<em>D = (1/2) * μ</em>n <em> Cox </em> (W/L) * (Vgs - Vth)^2

對(duì)于M1: Iref = (1/2) <em> μ_n </em> Cox <em> (W1/L) </em> (Vgs1 - Vth)^2

對(duì)于M2: Iref = (1/2) <em> μ_n </em> Cox <em> (n</em>W1/L) * (Vgs2 - Vth)^2

由于電流相等,聯(lián)立兩式可得:(Vgs1 - Vth)^2 = n <em> (Vgs2 - Vth)^2 => Vgs1 - Vth = sqrt(n) </em> (Vgs2 - Vth)

注意到M2源極有電阻R,其兩端電壓即為ΔVgs = Vgs1 - Vgs2。

通過(guò)代數(shù)變換,可以解出:ΔVgs = Vgs1 - Vgs2 = Vth <em> (sqrt(n) - 1) / sqrt(n) + (1/sqrt(n)) </em> sqrt(2<em>Iref/(μ_n</em>Cox<em>(W1/L))) </em> (sqrt(n)-1)

實(shí)際上,更直觀且常用的近似是,當(dāng)M1和M2的電流密度不ΔVgs近似正比于熱電壓VT(kT/q)乘以某個(gè)系數(shù)。但更精確的推導(dǎo)揭示了其與工藝參數(shù)和絕對(duì)電流的關(guān)系。

流過(guò)電阻R的電流即為Iref:Iref = ΔVgs / R

關(guān)鍵洞察:

- Iref 由 ΔVgs(一個(gè)相對(duì)穩(wěn)定的電壓,與絕對(duì)工藝參數(shù)弱相關(guān))和電阻R決定。

- R的絕對(duì)值變化(工藝偏差)會(huì)直接影響Iref的絕對(duì)值精度。因此,高性能基準(zhǔn)源常使用高精度外接電阻或精心設(shè)計(jì)的片上電阻(如硅化物阻擋多晶硅電阻)。

- 電源電壓的變化主要通過(guò)確保M1、M2始終處于飽和區(qū)來(lái)抑制其對(duì)Iref的影響,這要求一定的電源電壓余度(headroom)。

三、 從手算到仿真:Analog/RF IC設(shè)計(jì)流程

手算提供了起點(diǎn)和直覺(jué),但現(xiàn)代IC設(shè)計(jì)離不開(kāi)精細(xì)的仿真驗(yàn)證。完整流程包括:

- 架構(gòu)設(shè)計(jì)與手算:確定基準(zhǔn)源類(lèi)型(Bandgap、ΔVgs、自偏置等)、輸出阻抗、功耗、面積目標(biāo)。

- 電路搭建與DC仿真:在Cadence Virtuoso等EDA工具中搭建電路,進(jìn)行DC工作點(diǎn)分析,驗(yàn)證手算結(jié)果,調(diào)整器件尺寸使晶體管處于正確工作區(qū)。

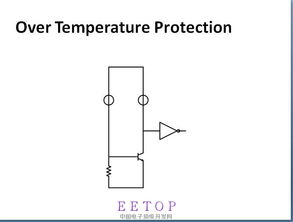

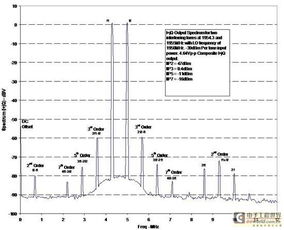

- 穩(wěn)定性與瞬態(tài)分析:基準(zhǔn)源作為偏置電路,必須穩(wěn)定。需進(jìn)行穩(wěn)定性(STB)分析,確保環(huán)路相位裕度足夠(通常>60°),并進(jìn)行瞬態(tài)仿真觀察啟動(dòng)特性和對(duì)電源擾動(dòng)的響應(yīng)。

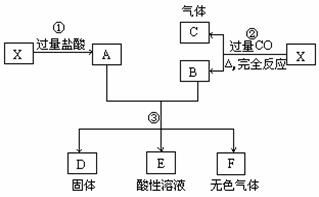

- 工藝角與蒙特卡洛分析:在TT(典型)、FF(快)、SS(慢)、SF、FS等工藝角下仿真,驗(yàn)證Iref在工藝偏差下的變化范圍。蒙特卡洛分析則進(jìn)一步模擬隨機(jī)失配(mismatch)的影響,這對(duì)電流鏡的匹配至關(guān)重要。

- 溫度特性分析:掃描溫度范圍(如-40°C到125°C),評(píng)估Iref的溫度系數(shù)(TC)。

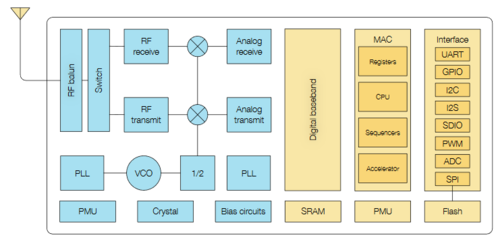

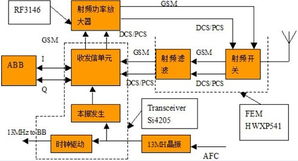

- 與負(fù)載電路的協(xié)同仿真:將基準(zhǔn)源代入其驅(qū)動(dòng)的實(shí)際電路(如LNA、Mixer、VCO)中,驗(yàn)證整體性能。

四、 EETop:匯聚智慧,共同探討

在Analog/RF IC設(shè)計(jì)的漫長(zhǎng)道路上,工程師絕非孤軍奮戰(zhàn)。EETop作為全球最大最火的半導(dǎo)體、集成電路、嵌入式設(shè)計(jì)社區(qū)之一,扮演著至關(guān)重要的角色:

- 知識(shí)寶庫(kù):論壇積累了海量的技術(shù)帖子,從“如何手算一個(gè)簡(jiǎn)單的電流鏡”到“毫米波PA的線性化技術(shù)”,應(yīng)有盡有。許多經(jīng)典問(wèn)題都能找到深入討論。

- 問(wèn)題求解平臺(tái):當(dāng)設(shè)計(jì)遇到瓶頸——例如,基準(zhǔn)電流在某個(gè)工藝角下偏差過(guò)大,或啟動(dòng)電路出現(xiàn)振蕩——在EETop發(fā)帖求助,往往能獲得來(lái)自業(yè)界資深工程師和同行們的寶貴經(jīng)驗(yàn)與思路。

- 前沿信息窗口:社區(qū)分享最新的行業(yè)動(dòng)態(tài)、會(huì)議(如ISSCC, VLSI)論文解讀、工具使用技巧以及招聘信息,幫助從業(yè)者緊跟技術(shù)潮流。

- 經(jīng)驗(yàn)交流與傳承:許多匿名用戶(hù)分享的“踩坑”記錄和解決方案,是最接地氣、最實(shí)用的學(xué)習(xí)材料,加速了新手工程師的成長(zhǎng)。

五、

手算基準(zhǔn)電流源,是叩開(kāi)Analog/RF IC設(shè)計(jì)大門(mén)的一塊敲門(mén)磚。它代表的是一種深入底層、追求本質(zhì)的工程師思維。從紙上公式到硅上電路,從個(gè)人手算到社區(qū)共研,Analog/RF IC設(shè)計(jì)是一場(chǎng)需要嚴(yán)謹(jǐn)、耐心與開(kāi)放協(xié)作的持久旅程。掌握手算基本功,善用EETop等社區(qū)資源,不斷在實(shí)踐中學(xué)習(xí)與反思,是每一位志在模擬射頻集成電路領(lǐng)域的工程師成長(zhǎng)的必經(jīng)之路。