在當今高度集成的電子系統中,模擬射頻(RF)集成電路(IC)扮演著至關重要的角色,廣泛應用于無線通信、雷達、物聯網和消費電子等領域。隨著工藝尺寸的不斷縮小和性能要求的日益提高,芯片的功耗密度顯著增加,使得熱管理成為設計中的關鍵挑戰之一。過溫保護(OTP)電路作為保障芯片可靠性和安全性的重要機制,在模擬射頻IC設計中不可或缺。本文將圍繞模擬射頻IC中的過溫保護設計進行討論,并結合EETop等專業社區中常見的設計思路與挑戰展開分析。

一、過溫保護的重要性與基本原理

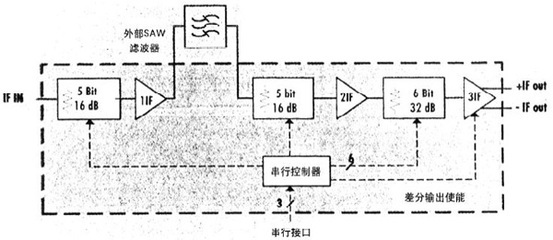

模擬射頻IC,尤其是功率放大器(PA)、低噪聲放大器(LNA)、混頻器等模塊,在工作時會產生大量熱量。若芯片溫度超過工藝允許的最大結溫(通常為125°C至150°C),可能導致性能退化、壽命縮短甚至永久性損壞。過溫保護電路通過監測芯片溫度,在檢測到過熱時自動采取保護措施,如降低偏置電流、關閉部分電路或觸發報警信號,從而防止熱失控。

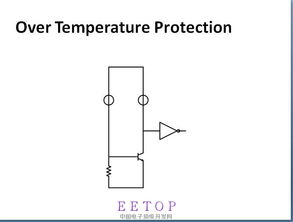

基本原理通常基于溫度傳感器(如帶隙基準源、二極管或熱敏電阻)和比較器電路。傳感器將溫度轉換為電壓信號,與預設的參考電壓比較,當溫度超過閾值時,輸出保護信號。在射頻設計中,需特別考慮保護電路的引入對高頻性能(如噪聲系數、線性度)的影響。

二、模擬射頻IC過溫保護的設計挑戰

- 精度與響應速度的平衡:過溫保護需要快速響應溫度變化,但傳感器和比較器的延遲可能影響實時性。閾值精度需控制在±5°C以內,以避免誤觸發或保護不足。在射頻環境中,溫度傳感器本身可能受電磁干擾,需通過屏蔽和濾波增強魯棒性。

- 與射頻性能的兼容性:過溫保護電路通常集成在芯片的模擬或數字部分,但其布局布線需遠離敏感射頻路徑,防止引入噪聲或耦合干擾。例如,在功率放大器設計中,保護電路的電源和地線應獨立隔離,避免影響輸出功率和效率。

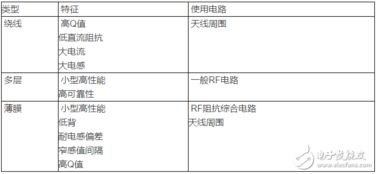

- 工藝與溫度變化的影響:半導體工藝的偏差(如CMOS或GaAs工藝)會導致溫度傳感器特性漂移。設計時需采用工藝角分析和溫度補償技術,確保閾值在不同工藝批次和溫度范圍內穩定。EETop社區中常討論的“trimming”技術(如激光修調或數字校準)可有效提升精度。

- 功耗與面積約束:過溫保護電路本身應低功耗,避免加重熱負荷。在面積受限的射頻芯片中,需優化傳感器和比較器的尺寸,例如利用現有電路(如偏置網絡)復用溫度傳感功能。

三、設計實踐與EETop社區見解

EETop作為國內最大的半導體和集成電路設計社區,匯集了大量工程師的實際經驗。在模擬射頻IC過溫保護設計中,常見實踐包括:

- 分布式溫度傳感:在芯片熱點區域(如功率晶體管附近)放置多個傳感器,實現更全面的監測,避免局部過熱漏檢。

- 自適應保護策略:結合數字控制電路,根據工作模式動態調整溫度閾值。例如,在高功率模式下降低閾值以提前保護,而在待機模式下提高閾值以減少誤觸發。

- 仿真與測試驗證:利用Cadence、ADS等工具進行電熱協同仿真,分析保護電路在瞬態和穩態下的行為。測試中需模擬極端環境,如高溫 chamber 測試,驗證保護響應的可靠性。

社區討論還強調,過溫保護不應孤立設計,而需與整體熱管理方案(如封裝散熱、PCB布局)協同。例如,在嵌入式系統中,射頻IC的過溫信號可反饋至主控制器,調整系統功耗或啟動風扇冷卻。

四、未來趨勢與

隨著5G、毫米波等技術的發展,模擬射頻IC將面臨更高頻率和更嚴苛的熱挑戰。過溫保護設計正朝著智能化、集成化方向演進,例如與片上機器學習模塊結合,實現預測性熱管理。新材料(如氮化鎵GaN)的應用也要求保護電路適配更高的溫度范圍。

過溫保護是模擬射頻IC設計中不可忽視的一環,它平衡了性能與可靠性。通過借鑒EETop等社區的經驗,并持續優化設計方法,工程師可以開發出更健壯、高效的射頻芯片,推動半導體行業在無線通信和嵌入式電子領域的進步。