在移動通信網絡飛速發展的今天,射頻(RF)集成電路作為連接數字世界與無線電磁波的關鍵橋梁,其性能直接決定了通信設備的速度、效率與可靠性。混合信號RF集成電路,集成了模擬RF前端與數字基帶處理,是現代通信芯片的核心。隨著通信標準向5G Advanced及6G演進,對帶寬、線性度、噪聲和功耗等指標提出了近乎嚴苛的要求,改進其RF性能已成為行業技術攻關的焦點。

一、 核心挑戰:性能瓶頸與干擾

改進混合信號RF電路性能,首先需直面其固有挑戰:

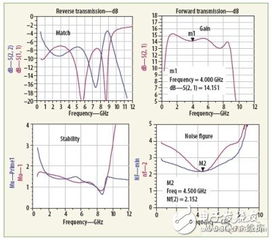

- 噪聲與靈敏度:在接收路徑,低噪聲放大器(LNA)的噪聲系數(NF)直接限制了系統的接收靈敏度。模擬電路中的閃爍噪聲(1/f噪聲)和熱噪聲在深亞微米工藝下更為顯著。

- 線性度與動態范圍:發射功率放大器(PA)的線性度(如IP3)必須足夠高,以處理高峰均比(PAPR)的現代調制信號(如OFDM),避免頻譜再生和鄰道干擾。系統需在強干擾信號下保持對小信號的接收能力,即擁有高動態范圍。

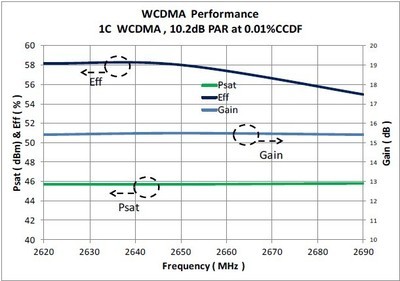

- 功耗與效率:尤其是在基站和移動終端中,PA的效率(如功率附加效率PAE)至關重要,直接影響設備續航和散熱設計。

- 集成度與隔離度:數字電路(如高速時鐘和數據轉換器)與敏感的模擬RF電路集成在同一芯片上,數字開關噪聲(地彈、電源噪聲)極易通過襯底耦合和電源線耦合干擾RF信號,導致性能劣化。

- 工藝限制:先進CMOS工藝雖提升了數字電路的密度與速度,但晶體管的截止頻率(fT)和擊穿電壓等模擬特性并未同步線性提升,對設計高功率、高頻RF電路構成約束。

二、 關鍵技術改進方向

針對上述挑戰,業界從架構、電路設計和工藝協同等多維度進行創新:

1. 先進的系統架構

- 數字輔助射頻技術:利用數字校準和預失真(DPD)技術,在數字域補償PA的非線性與記憶效應,顯著提升線性度和效率。同樣,數字校準可用于校正數據轉換器(ADC/DAC)的失配和頻率響應。

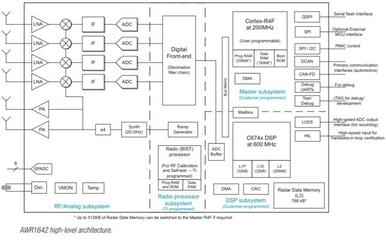

- 軟件定義無線電(SDR)與可重構架構:通過軟件配置射頻前端參數,使單一硬件平臺支持多頻段、多模式,并通過算法優化實時調整性能權衡。

2. 電路級創新設計

- 低噪聲與高線性度電路拓撲:探索如噪聲抵消技術、電流復用技術、互補衍生結構等,在功耗不變的前提下優化NF和IP3。對于PA,采用Doherty、包絡跟蹤(ET)等高效架構已成為主流。

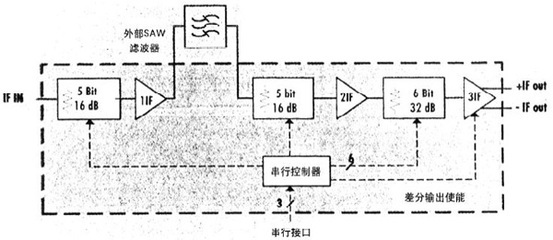

- 高性能數據轉換器:設計高精度、高采樣率的RF-DAC和RF-ADC,推動射頻信號鏈進一步“數字化”,減少對復雜模擬濾波器的依賴。采用時間交織、噪聲整形等技術提升性能。

- 電源與偏置優化:采用低壓差線性穩壓器(LDO)、開關電容穩壓器或包絡調制電源,為RF關鍵模塊提供“清潔”、高效的供電,抑制電源噪聲。

3. 版圖、封裝與隔離技術

- 版圖隔離策略:采用深N阱、保護環、隔離槽(如SOI工藝中的氧化埋層)等技術,增加數字與模擬/RF電路之間的襯底隔離。關鍵RF走線使用頂層厚金屬,并注重屏蔽和阻抗匹配。

- 先進封裝集成:采用扇出型晶圓級封裝(Fan-Out WLP)、系統級封裝(SiP)或硅橋技術,將優化的RF芯片(可能采用GaAs、SiGe等特殊工藝)與數字核心芯片異構集成,實現性能與成本的最佳平衡,同時減少片內干擾。

4. 工藝與建模協同

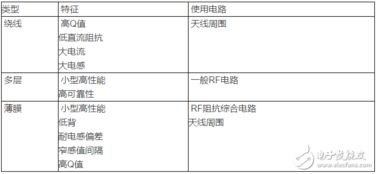

- FD-SOI與RF CMOS工藝:全耗盡型絕緣體上硅(FD-SOI)工藝因其出色的背面偏置控制能力和更低的寄生電容,在低功耗、高性能RF設計中展現出優勢。RF CMOS工藝庫則提供經過充分表征的射頻無源器件(如高品質因數Q的電感、變容二極管)和精確的射頻模型。

- 協同設計與仿真:建立包含封裝寄生參數、版圖電磁效應(EM)的系統級仿真環境,實現從系統架構到晶體管級的全鏈路協同優化,提前預知并解決潛在的信號完整性和干擾問題。

三、 與展望

改進混合信號RF集成電路的RF性能是一項系統工程,它不再僅僅是模擬電路設計師的職責,而是需要系統架構師、數字算法工程師、版圖設計師和工藝工程師的深度協同。隨著人工智能/機器學習技術的引入,有望實現RF性能的自主在線優化與故障預測。面向太赫茲頻段的6G通信,基于III-V族化合物半導體與硅基CMOS的異質集成技術,將成為突破性能極限的關鍵路徑。通過持續的技術融合與創新,混合信號RF IC將持續為移動通信網絡注入更強大、更智能的無線連接能力。