隨著無線通信技術的飛速發展,射頻(RF)集成電路在現代通信系統中扮演著關鍵角色。其中,差分電路因其出色的抗干擾能力和信號完整性,被廣泛應用于RF前端設計。本文將從差分電路的基本原理出發,探討其在現代通信系統中的設計方法,并重點分析其性能指標及優化策略。

一、差分電路的基本原理與優勢

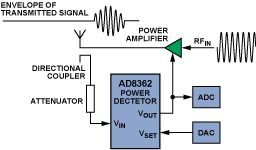

差分電路通過處理兩個相位相反的信號來實現信號的傳輸與處理。在RF集成電路中,這種結構能有效抑制共模噪聲,提高系統的信噪比(SNR)。例如,在低噪聲放大器(LNA)和混頻器等模塊中,差分設計可以減少電源噪聲和 substrate 耦合的影響,從而提升整體系統的可靠性。差分電路還能降低偶次諧波失真,這在寬帶通信系統中尤為重要。

二、差分電路的設計方法

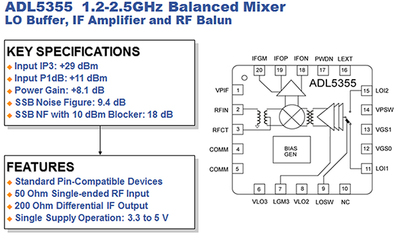

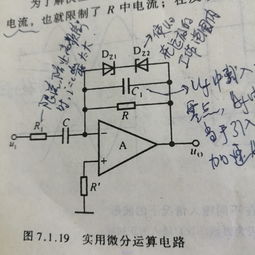

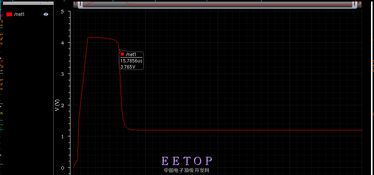

在RF集成電路中,差分電路的設計需綜合考慮阻抗匹配、線性度和功耗等因素。設計者需采用對稱布局以減少相位和幅度不平衡,常見技術包括使用巴倫(Balun)進行單端到差分的轉換。晶體管的選擇和偏置點設置對電路性能至關重要;例如,在差分對管設計中,采用 cascode 結構可提高增益和隔離度。通過仿真工具(如ADS或Cadence)進行參數優化,確保電路在目標頻段(如Sub-6 GHz或毫米波)內實現穩定的性能。

三、性能分析關鍵指標

差分電路的性能評估通常聚焦于以下幾個指標:

- 差模增益與共模抑制比(CMRR):高CMRR是差分電路的核心優勢,需通過精確的匹配和反饋網絡實現。

- 噪聲系數(NF):在接收機應用中,低噪聲設計能顯著提升靈敏度。差分結構通過抵消共模噪聲,有助于降低整體NF。

- 線性度(如IP3):現代通信系統要求高線性度以處理多載波信號,差分電路通過對稱設計可改善非線性失真。

- 功耗與集成度:隨著5G和物聯網的發展,低功耗和小型化成為設計重點,差分電路在CMOS工藝中的集成能力使其成為理想選擇。

四、優化策略與未來趨勢

為了進一步提升差分電路的性能,設計者可采用自適應偏置、數字輔助校準等技術來補償工藝變化和溫度漂移。在毫米波頻段,差分傳輸線和諧振結構的設計需考慮寄生效應和損耗。未來,隨著硅基RFIC和III-V族化合物半導體的融合,差分電路將在6G通信、雷達和衛星系統中發揮更大作用,推動通信系統向更高頻率和更低功耗發展。

差分電路是現代RF集成電路設計的基石,其抗干擾和高線性特性使其在通信系統中不可或缺。通過精細化設計和多維度性能分析,我們可以不斷優化差分電路,以滿足未來通信技術日益增長的需求。